# Lecture Notes in Computer Science

5568

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Alfred Kobsa

University of California, Irvine, CA, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Matthias S. Müller Bronis R. de Supinski Barbara M. Chapman (Eds.)

# Evolving OpenMP in an Age of Extreme Parallelism

5th International Workshop on OpenMP, IWOMP 2009 Dresden, Germany, June 3-5, 2009 Proceedings

#### Volume Editors

Matthias S. Müller

Technische Universität Dresden

Zentrum für Informationsdienste und Hochleistungsrechnen

01062 Dresden, Germany

E-mail: matthias.mueller@tu-dresden.de

Bronis R. de Supinski Lawrence Livermore National Laboratory Center for Applied Scientific Computing Livermore, CA 94551-0808, USA E-mail: bronis@llnl.gov

Barbara M. Chapman University of Houston Department of Computer Science Houston, TX 77204-3475, USA E-mail: chapman@cs.uh.edu

Library of Congress Control Number: Applied for

CR Subject Classification (1998): D.1, C.1, F.1, G.4, C.2.4, D.2.5, D.3.2, D.4.7

LNCS Sublibrary: SL 2 – Programming and Software Engineering

ISSN 0302-9743

ISBN-10 3-642-02284-7 Springer Berlin Heidelberg New York ISBN-13 978-3-642-02284-5 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

springer.com

© Springer-Verlag Berlin Heidelberg 2009 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12695836 06/3180 5 4 3 2 1 0

#### **Preface**

OpenMP is an application programming interface (API) that is widely accepted as a de facto standard for high-level shared-memory parallel programming. It is a portable, scalable programming model that provides a simple and flexible interface for developing shared-memory parallel applications in Fortran, C, and C++. Since its introduction in 1997, OpenMP has gained support from the majority of high-performance compiler and hardware vendors. Under the direction of the OpenMP Architecture Review Board (ARB), the OpenMP specification is undergoing further improvement. Active research in OpenMP compilers, runtime systems, tools, and environments continues to drive OpenMP evolution. To provide a forum for the dissemination and exchange of information about and experiences with OpenMP, the community of OpenMP researchers and developers in academia and industry is organized under cOMPunity (www.compunity.org). This organization has held workshops on OpenMP since 1999.

This book contains the proceedings of the 5th International Workshop on OpenMP held in Dresden in June 2009. With sessions on tools, benchmarks, applications, performance and runtime environments it covered all aspects of the current use of OpenMP. In addition, several contributions presented proposed extensions to OpenMP and evaluated reference implementations of those extensions. An invited talk provided the details on the latest specification development inside the Architecture Review Board. Together with the two keynotes about OpenMP on hardware accelerators and future generation processors it demonstrated that OpenMP is suitable for future generation systems.

OpenMP 3.0 has been adopted rapidly, as is evidenced by the number of available compilers and the use of new features by application developers. The OpenMP workshop series has made important contributions to the development of the specification and its adoption. This year's contributions clearly indicate that this role will continue in the future.

June 2009

Matthias S. Müller Barbara M. Chapman Bronis R. de Supinski

# Organization

#### Committee of IWOMP 2009

#### General Chair

Matthias S. Müller University of Dresden, Germany

#### Program Committee Chair

Matthias S. Müller University of Dresden, Germany

#### Program Committee

Dieter an Mey RWTH Aachen University, Germany

Eduard Ayguade CIRI, UPC, Spain

Mark Bull EPCC, University of Edinburgh, UK

Barbara Chapman University of Oregon, USA

Bronis R. de Supinski LLNL, USA

Rudolf Eigenmann Purdue University, USA Guang Gao University of Delaware, USA

Rick Kufrin NCSA, USA Chunhua Liao LLNL, USA

Federico Massaioli CASPUR, Rome, Italy

Lawrence Meadows Intel, USA

Mitsuhisa Sato University of Tsukuba, Japan

Ruud van der Pas Sun Microsystems, Geneva, Switzerland

Michael Wong IBM, Canada

#### Steering Committee Chair

Bronis R. de Supinski NNSA ASC, LLNL, USA

#### Steering Committee

Dieter an Mey CCC, RWTH Aachen University, Germany Eduard Ayguade Barcelona Supercomputing Center (BSC),

Spain

Mark Bull EPCC, UK

Barbara Chapman CEO of cOMPunity, Houston, USA

Rudolf Eigenmann Purdue University, USA Guang Gao University of Delaware, USA

Ricky Kendall ORNL, USA

Michaël Krajecki University of Reims, France

Rick Kufrin NCSA, USA

Federico Massaioli CASPUR, Rome, Italy

#### VIII Organization

Lawrence Meadows KSL Intel, USA

Matthias S. Müller University of Dresden, ZIH, Germany

Arnaud Renard University of Reims, France Mitsuhisa Sato University of Tsukuba, Japan

Sanjiv Shah Intel, USA

Ruud van der Pas Sun Microsystems, Geneva, Switzerland

Matthijs van Waveren Fujitsu, France Michael Wong IBM, Canada

Weimin Zheng Tsinghua University, China

# **Table of Contents**

# Fifth International Workshop on OpenMP IWOMP 2009

| Performance and Applications                                                                        |    |

|-----------------------------------------------------------------------------------------------------|----|

| Parallel Simulation of Bevel Gear Cutting Processes with OpenMP Tasks                               | 1  |

| Evaluation of Multicore Processors for Embedded Systems by Parallel Benchmark Program Using OpenMP  | 15 |

| Extending Automatic Parallelization to Optimize High-Level Abstractions for Multicore               | 28 |

| Scalability Evaluation of Barrier Algorithms for OpenMP                                             | 42 |

| Use of Cluster OpenMP with the Gaussian Quantum Chemistry Code: A Preliminary Performance Analysis  | 53 |

| Runtime Environments                                                                                |    |

| Evaluating OpenMP 3.0 Run Time Systems on Unbalanced Task Graphs                                    | 63 |

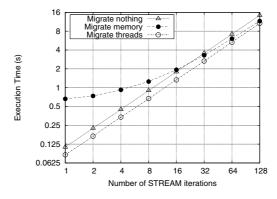

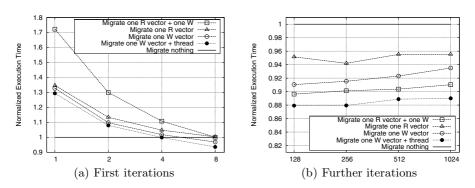

| Dynamic Task and Data Placement over NUMA Architectures: An OpenMP Runtime Perspective              | 79 |

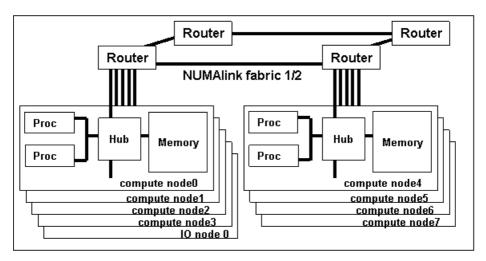

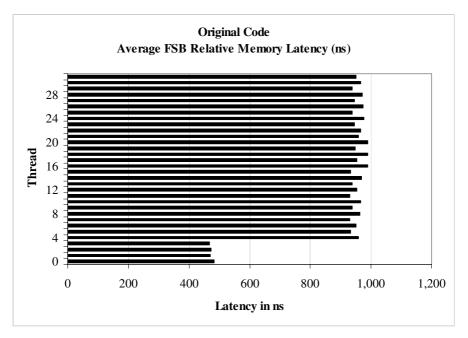

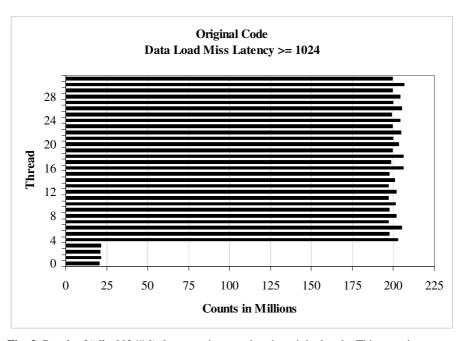

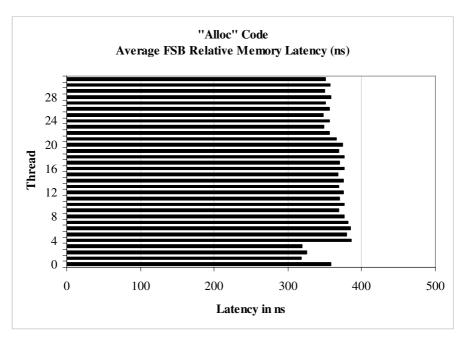

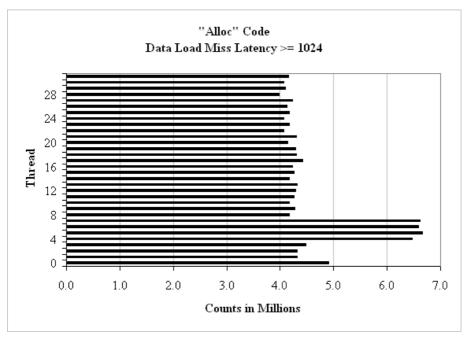

| Scalability of Gaussian 03 on SGI Altix: The Importance of Data<br>Locality on CC-NUMA Architecture | 93 |

| Tools and Benchmarks                                                          |     |

|-------------------------------------------------------------------------------|-----|

| Providing Observability for OpenMP 3.0 Applications                           | 104 |

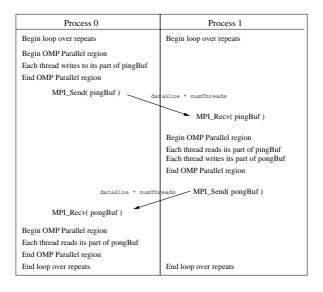

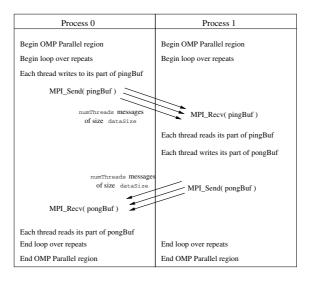

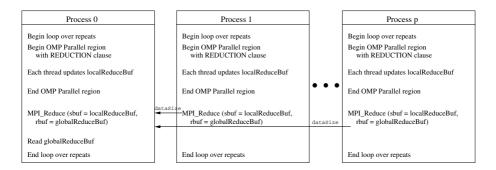

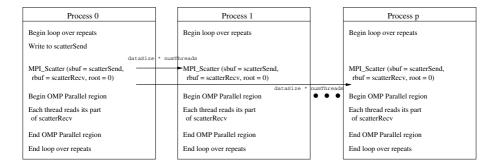

| A Microbenchmark Suite for Mixed-Mode OpenMP/MPI                              | 118 |

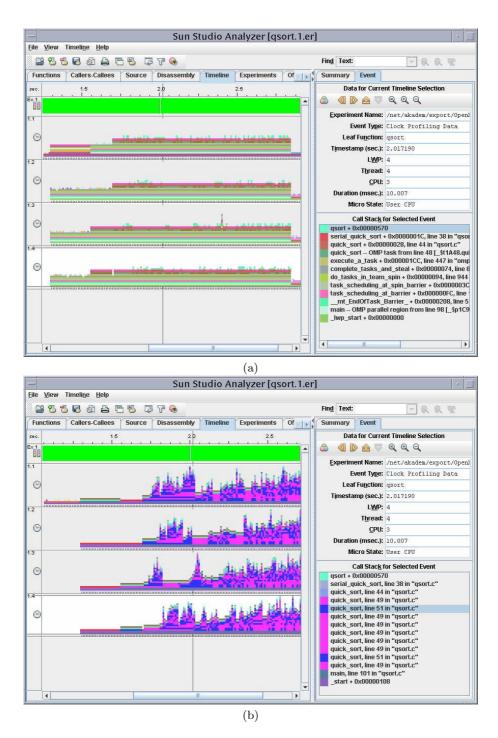

| Performance Profiling for OpenMP Tasks                                        | 132 |

| Proposed Extensions to OpenMP                                                 |     |

| Tile Reduction: The First Step towards Tile Aware Parallelization in OpenMP   | 140 |

| A Proposal to Extend the OpenMP Tasking Model for Heterogeneous Architectures | 154 |

| Identifying Inter-task Communication in Shared Memory Programming Models      | 168 |

| Author Index                                                                  | 183 |

# Parallel Simulation of Bevel Gear Cutting Processes with OpenMP Tasks

Paul Kapinos and Dieter an Mey

Center for Computing and Communication, JARA, RWTH Aachen University, Germany {kapinos,anmey}@rz.rwth-aachen.de

**Abstract.** Modeling of bevel gear cutting processes requires highly flexible data structures and algorithms. We compare OpenMP3.0 tasks with previously applied approaches like nesting parallel sections and stack based algorithms when parallelizing recursive procedures written in Fortran 95 working on binary tree structures.

**Keywords:** OpenMP 3.0, Tasking, Nesting, Fortran 90/95, Recursive Subroutines, Parallelization.

#### 1 Introduction

Today manufacturers of bevel gears are confronted with continuously growing demands for cost effectiveness of the manufacturing process. This is also true for the cutting of bevel gears. To enhance the productivity of the manufacturing processes, the processing time has to be reduced. In order to further improve productivity, the tool life has to be maximized so that the tooling time and the tool costs are minimized. By increasing the cutting velocity, a reduction in the primary processing time is obtained. This results in an increased load on the cutting edge of the tool. In order to predict the tool life during these processes, a detailed analysis of the cutting process is required to evaluate the chip creation conditions. The Laboratory for Machine Tools and Production Engineering (WZL, [1]) of the RWTH Aachen University develops the program KEGELSPAN [2] [3] [4] to simulate and study the manufacturing process of bevel gears.

Shared-memory parallelization with OpenMP was taken into account during the development of Kegelspan early on. OpenMP was chosen because of the possibility to gradually adopt parallelism on parts of premature program versions without rewriting lots of code, and the ability to easily handle complicated data structures. The recursive routines, which work on binary trees, were detected to consume a substantial part of the runtime in initial versions of Kegelspan and have been investigated and parallelized in [5]. In this paper we expand this work taking the long-awaited OpenMP 3.0 tasking approach into consideration.

In section 2 we briefly describe the program KEGELSPAN [2]. In section 3 we discuss the parallelization strategies which we applied to the recursive routines,

which have been selected for parallelization after profiling the whole program. We present and discuss our performance measurements of the parallelized routines in section 4 and conclude in section 5.

#### 2 Simulation of Bevel Gear Cutting Processes

The program Kegelspan developed by the WZL [1] simulates bevel gear cutting with defined cutting edges. It is written in Fortran 95 heavily using many advanced language features like modules, recursive functions, Fortran pointers and operator overloading. In theory, the process of a single cutting process is well understood, but the production of a complete bevel gear consists of a series of cutting processes. By today's standards the tool wear, life time and critical wear behavior are determined experimentally. The target of the development of Kegelspan is to determine optimal process attributes (cutting speed, feed etc.) on the basis of calculated variables like chip thickness, unwinded cutting edge length and to better predict the tool wear behavior.

The tool's edges are represented by spacial lines. The kinetics of the movements of the cutting tool determines the movement of these lines in space and defines the hulls of the cutting edges.

These hulls, represented by a three-dimensional polygon grid, are examined in the order of the cutting edges for penetration with the polygon grid of the workpiece. If a penetration occurs, the difference volume, the so-called non-deformed chip, is computed by subtracting the surfaces of both polygon grids. Based on the non-deformed chip, the characteristic values can be determined. Whenever the individual cuts are computed, the polygon network of the workpiece is adaptively refined. This frequently leads to an unbalanced distribution of nodes and polygons in space.

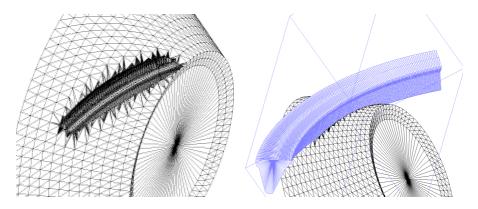

In order to reduce the amount of computation by only examining neighboring parts of the polygon grids for mutual penetration, a binary space partitioning tree (BSP tree) is constructed. The polygons are recursively sorted into a hierarchy of nested axis aligned bounding boxes (AABBs), until the number of polygons per box falls below an adjustable threshold value. Because of the uneven distribution of the nodes in space (see figure 1 left) the binary tree (BSP Tree) tends to be quite unbalanced. However, an attempt to balance this tree according to the number of polygons per sub-box by setting the split plane through the mass center of all polygons turned out to be counter-productive. For geometrical and algorithmic reasons the program's runtime increased considerably.

The BSP trees are implemented with dynamic data structures and Fortran pointers in the KEGELSPAN program and recursive routines are used for tree traversal. As early performance analyses revealed that 75 percent of the total runtime was consumed in these recursive procedures, they were initially parallelized with "traditional" OpenMP approaches and now with OpenMP 3.0 tasking constructs as soon as compilers became available.

Fig. 1. Adaptive refinement (left) and penetration of meshes (right)

#### 3 Parallelization of the Recursive Routines

For simplicity we only discuss routines which directly call themselves twice and are used for the traversal of binary trees, if these two evocations can safely be computed in parallel.

```

RECURSIVE SUBROUTINE BSPtraversal (tree)

TYPE (BSPtree) :: tree

.... do work here

CALL BSPtraversal (tree%left)

CALL BSPtraversal (tree%right)

END SUBROUTINE BSPtraversal

```

#### 3.1 Parallelization with Nested PARALLEL SECTIONS Constructs

In the first approach we simply executed both recursive evocations in a PAR-ALLEL SECTIONS constructs containing two sections:

```

RECURSIVE SUBROUTINE PrimerPar (tree)

TYPE (BSPtree) :: tree

.... do work here

!$OMP PARALLEL SECTIONS

!$OMP SECTION

CALL PrimerPar (tree%left)

!$OMP SECTION

CALL PrimerPar (tree%right)

!$OMP END PARALLEL SECTIONS ! <--- barrier !

END SUBROUTINE PrimerPar

```

In order to activate more than 2 threads, nested parallelism has to be supported by the compiler and explicitly enabled. If there is no limitation of the nesting depth or the total number of threads, an additional thread will be forked for each node of the tree. We applied two different strategies to avoid overloading the system with thousands of threads which could easily happen in <code>KEGELSPAN</code> program.

Limiting the nesting depth to N also implies that the total number of threads is limited by  $2^N$ . The computational load is distributed to the threads in a deterministic manner as the distribution is determined by the shape of the tree. If the subtrees differ in size, the tree is unbalanced and so is the work distribution. The OpenMP overhead is limited, as once the maximum nesting level is reached, the remaining subtree will be processed sequentially.

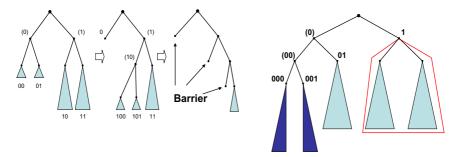

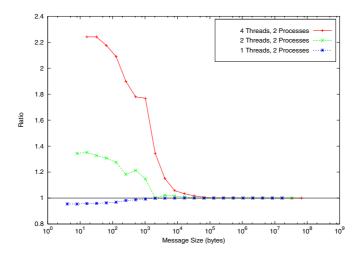

Limiting the total number of threads to M ("thread pool") also implies that the nesting level is limited by M-1. For each node the number of currently active threads is checked and as long as the limit is not reached, an additional thread is forked. This strategy potentially may lead to an automatic load balance. But, alas, the implied barrier at the end of the PARALLEL SECTIONS construct inserts additional overhead (see figure 2 left). Furthermore, the work distribution is non-deterministic such that even in the case of a balanced tree, a load imbalance may occur (see figure 2 right).

Up to version 2.5 of the OpenMP API there was no standard way to control the maximum nesting depth or the maximum number of threads of an OpenMP program. Although some compilers offered extensions to control the nesting behavior of applications we implemented this manually by using a variable which was decremented in every recursive call (limiting max. nested depth) or a shared variable containing the number of currently active threads (thread pool) in order to retain portability.

In OpenMP v3.0 new Internal Control Variables (ICV) allow to set the limits in a portable and easy way. The THREAD-LIMIT-VAR ICV may be controlled by the OMP\_THREAD\_LIMIT environment variable and is used to limit the size of the "thread pool". The MAX-ACTIVE-LEVELS-VAR ICV may be controlled by OMP\_MAX\_ACTIVE\_LEVELS environment variable and is used to limit the maximum nesting depth.

Fig. 2. Nested PARALLEL SECTIONS with 4 threads: The size of the triangles represents the amount of work in the subtrees.

Left: Limited self-balancing.

Right: Work scheduling is non-deterministic; bad scheduling on a balanced tree.

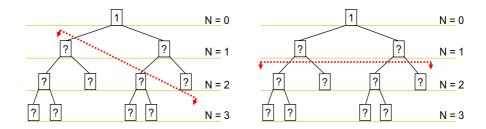

Fig. 3. Adaptive parallelization: Probability fronts for LIFO (left) or FIFO queue

#### 3.2 Adaptive Parallelization

In an alternative approach we reimplemented the recursive procedures by an iterative algorithm. A compiler would similarly map the recursion to a stack based algorithm. But only the manual approach provides an opportunity for parallelization. A dynamic data structure (LIFO- or FIFO queue) is introduced to dynamically store the arguments of the previously recursive procedure call. The initial parameters are stored into this structure in an initialization phase and a team of threads executes a parallel loop until the queue is empty and no thread is working on any item any more. Accesses to the queue have to be guarded in critical regions.

The participating threads get an item from the queue, proceed with their work, and eventually put items into the queue - if the recursive pendant would have recursive evocations here.

This adaptive algorithm leads to an automatically balanced work load as long as the tree is not degenerated into a list.

```

SUBROUTINE BSPstack (tree)

TYPE (BSPtree) :: tree

TYPE (Stack) :: myStack

.....

CALL StackPush (tree, myStack) ! Initialize

!$OMP PARALLEL

DO WHILE (queue is not empty .and. at least one thread is busy)

CALL StackPop (localtemp, myStack)

... work on localtemp here

IF ( node is not a leaf node )

CALL StackPush (localtemp%left, myStack)

CALL StackPush (localtemp%right, myStack)

END IF

END DO

!$OMP END PARALLEL

.....

END SUBROUTINE BSPstack

```

As the queue has to be accessed by all threads in critical regions, it may become a bottleneck for a large number of threads and thus lead to a limited scalability. An implementation of a distributed queue may alleviate overhead.

The strategy of the queue has an impact on the processing sequence of the nodes.

A FIFO approach corresponds to a breadth-first traversal when executed serially, whereas the LIFO approach corresponds to a depth-first traversal. In parallel, there is no arrangement of node traversal enforced, but the trends still remain (see fig. 3)

The programming effort for the adaptive algorithm is considerably higher compared to the one employing nested PARALLEL SECTIONS, as it may impact the implementation of the work function as well due to the paradigm change from recursive to iterative.

#### 3.3 Tasking

With OpenMP version 3.0 [6] the new tasking concept offers a thriving new alternative. A task is an enclosed computational assignment, which is defined first and executed later by any thread of the participating team. A task can even generate further tasks. After generating another task, the generating task can continue its execution first, while the generated task can be executed by any thread of the participating team immediately or later. At an (implicit or explicit) TASKWAIT barrier all previously generated tasks have to be completed.

Obviously, the tasking concept lends itself to the parallelization of recursive procedures by simply putting the recursive procedure evocation into task constructs.

A team of threads is forked and the master thread generates the first task to operate on the root node. Tasks which then are generated recursively, are equally executed by all threads of the team.

Here the TASKWAIT directive hardly affects performance, because threads arriving at this barrier can happily suspend execution and work on another task without any need to idle. This property of OpenMP tasks leads to an improved load balancing almost "for free".

```

. . . . .

!$OMP PARALLEL

IF (master) THEN CALL BSPtask (root) ! Start, one Thread only

!$OMP END PARALLEL

RECURSIVE SUBROUTINE BSPtask (tree)

TYPE (BSPtree) :: tree

.... do work here

!$OMP TASK

CALL BSPpar (tree%left)

!$OMP END TASK

!$OMP TASK

CALL BSPpar (tree%right)

!$OMP END TASK

!$OMP TASKWAIT ! <---

does not really affect performance !

END SUBROUTINE BSPtask

```

Usually a TASKWAIT barrier is necessary, if the output of a subtask is needed in the computation after the TASKWAIT directive. If this is not the case, as e.g. the subtask's output is stored in disjoint partitions of a shared memory region, there is the opportunity to save system resources because of a lower number of simultaneously active tasks. But it turns out that Fortran is at a disadvantage because Fortran pointers cannot be declared FIRSTPRIVATE on a TASK directive (see [6] section 2.9.3.4 on page 94) and without a TASKWAIT barrier, the variables' lifetime which are shared in the generating task might prematurely end (see [6] section 2.7 on page 61).

Additionally creating a task per tree node may lead to a slow-down due to the overhead of managing the tasks by the runtime system. A possible solution to this may be obtained by increasing the amount of work performed per task.

The merging of the work may be achieved by forbidding the spawning of additional tasks if an threshold nesting depth of tasks is reached. This may be implemented by an IF clause in the task definition or by a conventional if branch and calling the serial version of the routine. Furthermore, the call tree may be analyzed in more detail to handle tiny and fat nodes differently. The fat nodes can be sensibly parallelized by spawning an additional task, whereas tiny ones should be executed immediately.

#### 4 Performance Experiments

Two recursive subroutines of KEGELSPAN have been parallelized with all the approaches described in the previous section. We compare programming effort and report on runtime measurements on two different platforms.

#### 4.1 Work Distribution and Characteristics of the BSP Trees

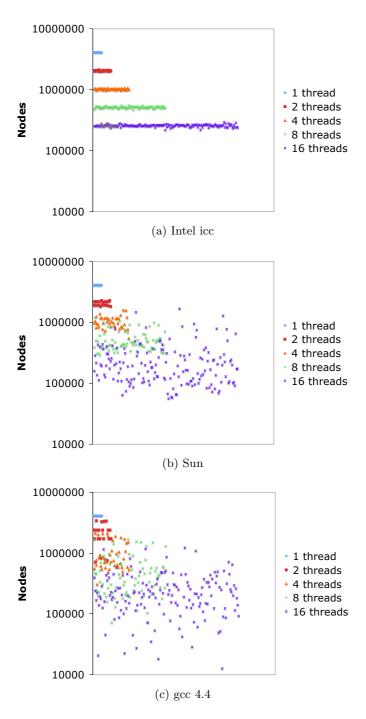

Because of algorithmic reasons (adaptive refinement of meshes and unequal distribution of points in the space) the BSP trees in KEGELSPAN are heavily unbalanced. Furthermore, the shape and the growth of the trees varies a lot during the execution of the program and are specific to the particular use case. Hence, only an averaged overview of the tree growth and shape may be given which is valid only for the test data set.

Accumulated over the whole computation, there are about 230 thousands of leaves and almost the same number of inner nodes in the BSP trees. The average leaf depth is 12, with a lot of leaves (63%) concentrated in the depth of 10 to 13. There are leaves in the depth from 6 to 20, too. On average, one subtree from the root node has about double the number of nodes than the other subtree, confirming that the trees are unbalanced.

The first of the parallelized routines, denoted as A, is an adopted variation of the well-known QuickSort algorithm. The amount of work decreases in every step and consequently the scalability of any parallelization of this algorithm is limited.

|                          | SECTIONS     | Adaptive parallelization | Tasking                 |

|--------------------------|--------------|--------------------------|-------------------------|

| time to adopt, est.      | 1 hour       | 1 week                   | 1 hour + "verification" |

| code lines added         | less than 50 | up to 1000               | less than 50            |

| work on unbalanced trees | bad          | good                     | good                    |

| algorithmical changes?   | no           | maybe                    | no                      |

Table 1. Three approaches in comparison

In the second parallelized routine, denoted as B, almost whole work is concentrated in the leaves of the BSP tree. The work of inner nodes consists only of some reduction to merge the results of recursive calls.

The execution time of an average task is in the order of milliseconds, or millions of CPU cycles.

#### 4.2 Programming Effort

We try to summarize and categorize our experiences in implementing the different parallelization approaches in table 1.

Parallelization with a nested **PARALLEL SECTIONS** construct was the simplest, because it is a simple and matured concept and it requires only few additional lines of code and no algorithmic changes.

The implementation of the adaptive parallelization algorithm required a complete rewrite of the related routines including some changes in the algorithm. Programming efforts and error-proneness were clearly higher.

The time to implement the tasking concept was comparable to the SECTIONS solution. But anyhow it took some time to verify the solution and to get the data scopes all right. The particular definition of default data scopes for the TASK construct compared to the PARALLEL construct (see [6] section 2.9.1.1 on page 79) leads to some confusion in determining the data scope used by default. Scoping seems to be a typical source of errors and we hope that the known data race detection tools will be ready to check task constructs soon.

The new runtime routines and the environment variables for the limitation of the nesting depth or the size of the thread pool provided by OpenMP 3.0 furthermore reduce the necessary programming effort. But they turned out to be less flexible than our hand-coded routines.

#### 4.3 Speedup

We ran all variants of the parallelized routines on two different machines:

- a Fujitsu-Siemens RX200 S4/X equipped with two Intel Xeon E5450 quad core processors at 3.0GHz running Linux (denoted as "Harpertown" in the following) and

- a Sun T5120 equipped with one eight-core Sun Niagara T2 processor with 64 simultaneous threads at 1.4 GHz running Solaris (denoted as "Niagara2").

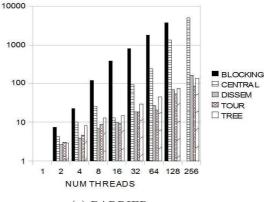

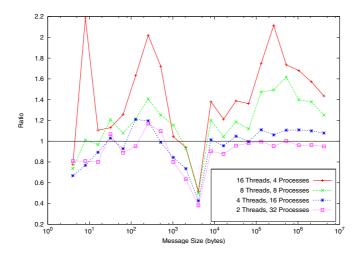

$\begin{tabular}{ll} \textbf{Table 2. Speedup compared to serial version, without thread binding. SD = SECTIONS with limiting the nesting depth, ST = SECTIONS with limiting the number of active threads (threadpool) , AF = adaptive parallelization with FIFO queue, AL = adaptive parallelization with LIFO queue (stack), T = tasking (without limits to task spawning). SD and ST employ our hand-coded versions to control the nesting behavior and not the new OpenMP 3.30 runtime functions. } \label{eq:table_control}$

|              |     |      | Niagara2 |       |        |       |                       | Harpertown |      |      |                                    |      |      |      |      |      |

|--------------|-----|------|----------|-------|--------|-------|-----------------------|------------|------|------|------------------------------------|------|------|------|------|------|

|              |     |      | SU       | JN St | udio l | Expre | ess $07/2008$ (-fast) |            |      |      | Intel 11.1.016 beta ( <b>-O3</b> ) |      |      |      |      |      |

| #"           | Thr | SD   | ST       | AF    | AL     | Τ     | SD                    | ST         | AF   | AL   | Т                                  | SD   | ST   | AF   | AL   | Τ    |

| ee           | 1   | 0.98 | 1.02     | 0.99  | 0.97   | 1.00  | 1.00                  | 1.00       | 0.96 | 0.97 | 0.99                               | 0.93 | 0.93 | 0.91 | 0.93 | 1.00 |

| SPTree       | 2   | 1.45 | 1.45     | 1.77  | 1.77   | 1.78  | 1.47                  | 1.46       | 1.38 | 1.67 | 1.71                               | 1.35 | 1.37 | 1.61 | 1.64 | 1.81 |

|              | 4   | 2.31 | 1.97     | 2.72  | 2.76   | 2.78  | 2.30                  | 1.94       | 2.52 | 2.61 | 2.53                               | 2.17 | 1.82 | 2.45 | 2.48 | 2.83 |

| buildB       | 8   | 2.64 | 2.34     | 3.39  | 3.39   | 3.47  | 2.53                  | 2.20       | 3.02 | 3.09 | 3.06                               | 2.41 | 2.37 | 2.89 | 2.93 | 3.49 |

| ui           | 16  | 2.98 | 2.70     | 3.69  | 3.69   | 3.81  | 2.63                  | 2.39       | 3.01 | 3.09 | 3.06                               |      |      |      |      |      |

| ·            |     |      |          | 3.59  |        | 3.83  |                       |            |      |      |                                    |      |      |      |      |      |

| Α            | 64  | 2.97 | 2.97     | 1.30  | 1.28   | 3.86  |                       |            |      |      |                                    |      |      |      |      |      |

| rr           | 1   | 1.01 | 0.98     | 1.12  | 1.12   | 0.53  | 0.95                  | 0.95       | 0.99 | 1.00 | 0.51                               | 0.99 | 0.99 | 0.94 | 0.94 | 0.49 |

| llA          | 2   | 1.41 | 1.42     | 1.83  | 2.00   | 0.98  | 1.02                  | 0.98       | 1.03 | 1.07 | 0.60                               | 1.20 | 1.19 | 1.44 | 1.52 | 0.82 |

| Sch          | 4   | 1.70 | 1.90     | 2.61  | 3.62   | 1.89  | 1.00                  | 0.99       | 0.91 | 0.88 | 0.51                               | 1.36 | 1.44 | 1.65 | 1.98 | 1.10 |

| Lp           | 8   | 1.94 | 2.18     | 3.86  | 6.01   | 3.53  | 0.97                  | 0.88       | 0.92 | 0.86 | 0.45                               | 1.43 | 1.69 | 1.54 | 1.82 | 1.06 |

| boxLpSchlArr | 16  | 2.93 | 2.19     | 5.39  | 8.59   | 5.98  | 0.91                  | 0.77       | 0.90 | 0.84 | 0.45                               |      |      |      |      |      |

|              |     |      |          | 6.57  | 8.30   | 7.96  |                       |            |      |      |                                    |      |      |      |      |      |

| В            | 64  | 2.78 | 1.56     | 4.74  | 4.87   | 8.01  |                       |            |      |      |                                    |      |      |      |      |      |

**Table 3.** Accumulated serial execution times of the recursive routines in seconds (corresponding to a speedup of 1.0 in table 2)

|                 | Niagara2 |                     |                     |

|-----------------|----------|---------------------|---------------------|

|                 | SUN Stuc | dio Express 07/2008 | Intel 11.0.034 beta |

| A: buildBSPTree | 157      | 17.9                | 16.6                |

| B: boxLpSchlArr | 501      | 54.9                | 38.8                |

On both Niagara2 and Harpertown we used the Sun Studio Express compiler and turned on high optimization with **-fast** whereas on Harpertown we additionally used the Intel Beta compiler (11.1.016) for which we were able to use the optimization with **-O3**, only if we omit the **-g** debug flag.

We observe a maximum speedup of 3.49 with 8 threads on Harpertown and 8.59 with 16 threads on Niagara2 (see tables 2). Please note the difference in absolute runtime (table 3): Because of the higher clock cycle, the superscalar architecture, and the large caches the Harpertown outperforms the Niagara2 by about one order of magnitude with the serial code version.

As Niagara2 contains 2 instruction units per core, 16 threads frequently are a sweet-spot for multi-threaded applications which do not demand a high memory bandwidth. The Niagara2 typically shines when running memory intensive codes with many (up to 64) threads waiting for memory in parallel. Here we obtain

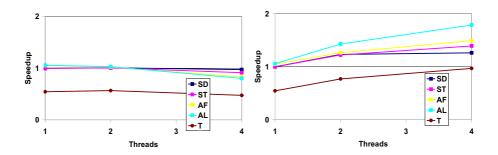

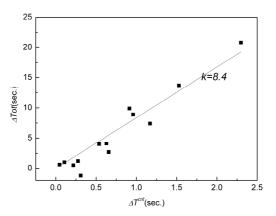

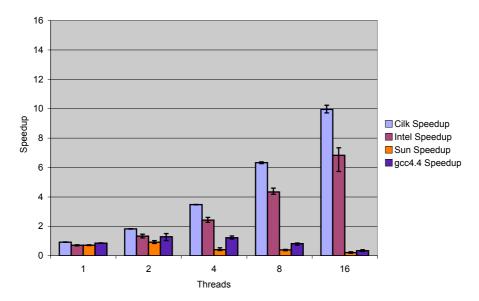

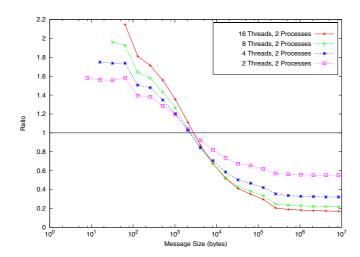

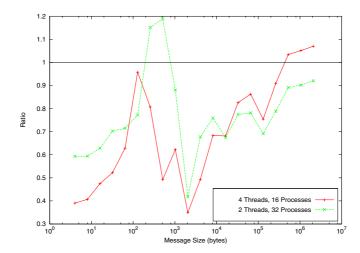

Fig. 4. Speedup on Dunnington with thread placement by taskset. Sun Studio compiler -fast.

Left: scatter - private cache (taskset -c 0,1,2,3)

Right: compact - shared cache (taskset -c 1,9,10,11,12,13)

a speedup of up to 3.86 with 64 threads on routine A and up to 8.59 with 16 threads on routine B. All program versions display a smooth behavior with respect to the number of threads employed, though the scalability of routine A is obviously limited.

On Harpertown, we frequently observed that 2 threads of a memory intensive code may consume the whole bandwidth of the front side bus while higher scalability can be observed for cache-friendly applications.

For KEGELSPAN a speedup of 3.49 (Intel compiler) or 3.09 (Sun Studio compiler) for the routine A with 8 threads is a tolerable result, in particular when taking the limited scalability of the QuickSort-like algorithm into account.

The parallel versions of routine B, that scaled up to 8.59 on Niagara2, do not perform well on Harpertown. The best speedup achieved with Intel compiler is about 2 with 4 threads. The Sun Studio compiled version fails to scale at all on Harpertown.

In order to get a better understanding of this observation, we run a limited number of tests on a 4-socket Intel Dunnington<sup>1</sup> processor based machine with the same Sun Studio binaries to focus on binding and caching effects. In one test setting we bound all (up to four) threads to one socket using **taskset**, such that all threads shared the same L3 cache. In the other test setting we pinned each thread to a separate socket and therefore the threads had their own large L3 cache.

In the runs with shared cache we obtained a speedup of up to 1.8 which is similar to speedup of the Intel compiler version (see fig. 4 right). If the threads runs each on own socket we again don't see any speedup.

We therefore assume that the low scalability of the routine B is a consequence of memory bus limitations and cache issues. Unfortunately, we were not yet able to conduct any useful hardware performance counter experiments (see below).

<sup>&</sup>lt;sup>1</sup> We choose a machine with 4 Intel Dunnington CPUs in comparison to a 2 socket Harpertown machine. Therefore it is possible to run up to 4 threads with a dedicated socket and thus without sharing cache.

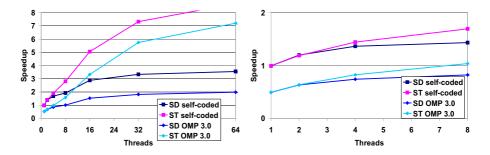

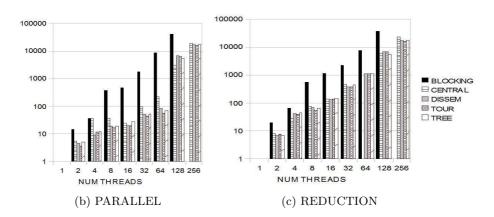

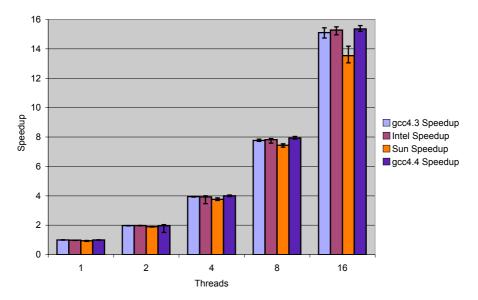

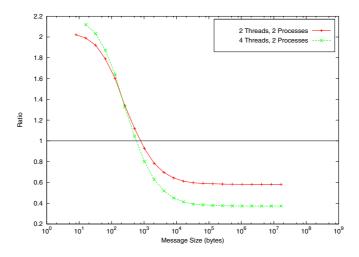

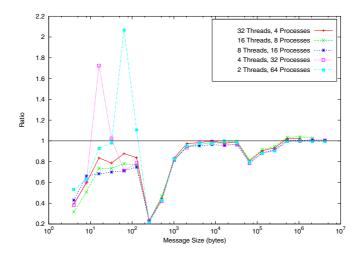

Fig. 5. Nested PARALLEL SECTIONS: Comparison of the self-coded and the OMP 3.0 driven implementations of thread forking boundaries on Routine B

Left: Niagara2, studio f90 express (-fast) Right: Xeon, ifort 11.1.016 (-O3)

# Evaluation of the new OpenMP 3.0 runtime functions to limit the maximum thread count in nested parallel SECTIONS

- The OpenMP 3.0 ICVs THREAD-LIMIT-VAR and MAX-ACTIVE-LEVELS-VAR are global the program, i.e. all simultaneous parallel regions share them. Furthermore there is no way to adjust the THREAD-LIMIT-VAR ICV from within the program (this ICV may be adjusted by setting the OMP\_THREAD\_LIMIT environment variable only) thus all parallel regions in the whole program share their value. Our own implementation is more flexible in adjustment of number of threads in parallel regions.

- The OpenMP 3.0 variants are potentially dangerous in use. Due to high default values of THREAD-LIMIT-VAR and MAX-ACTIVE-LEVELS-VAR for the tested compilers (e.g. 2147483647 for both ICVs by Intel compiler), simply neglecting to set an environment variable may lead to an heavily overloaded system or to running out of memory.

For routine A the performance of the hand-coded version and the OpenMP 3.0 runtime functions has been observed to be the same.

For routine B the OpenMP 3.0 implementation is approximately twice as slow as the hand-coded version (see fig. 5). Surprisingly, for this routine the tasking variant is also approx. two times slower with only one thread than the serial version. This behavior lets us draw the conclusion that there is an fundamental problem with this routine in combination with OpenMP 3.0. Here further research is needed.

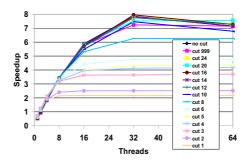

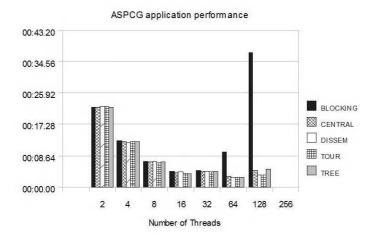

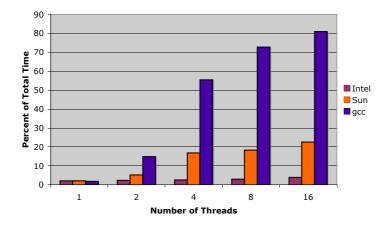

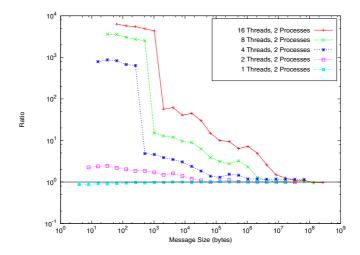

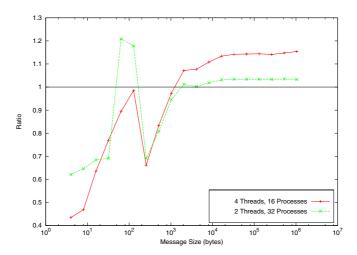

#### The impact of limiting the number of tasks was also investigated.

We implemented reducing the task number by limiting the maximum task nesting depth both with IF clauses in task definition and with Fortran conditional branches and calling the serial version of the routine. In routine B, in which the most work is concentrated in the leaves, we implemented also the

**Fig. 6.** Reducing the number of tasks by limiting the max. task nesting depth with Fortran conditional branching and calling the serial version of the routine. Niagara2, Routine B, Sun Studio f90 Express (-fast).

differentiation of inner nodes (for which no task were spawned) and leaves (which are outsourced to tasks).

We discovered that reducing the number of tasks does not result in any further speedup for KEGELSPAN. That is in contrast to the result reported in [7] when parallelizing the computation of Fibonacci numbers. We also see no overhead due to additional IF's if the cutting depth was chosen large enough to let the cutting condition always be false (and thus producing an task for every node in the tree). Only the slow-down due of advancing serialization and load imbalance was seen, if the cutting depth was decreasing, see fig. 6.

It seems that the task granularity in our program is considerably higher than the overhead of the runtime's task management.

In general, our performance measurements confirm that the tasking and adaptive approaches scale better than nested PARALLEL SECTIONS as the trees are unbalanced. Interestingly, in routine B the tasking approach is always much slower with few threads (a factor of two with a single thread) but it catches up when increasing the thread count. For the nested PARALLEL SECTIONS approach it is not clear whether limiting the nesting depth or the thread pool size is advantageous. For the adaptive parallelization the LIFO queue outperforms the FIFO queue for routine B, while for routine A the difference is negligible. The advantage of LIFO queue compared to FIFO seems to be evoked by better cache utilization. The last element put into the LIFO queue will probably immediately be processed, keeping the caches hot.

#### 4.4 Pitfalls

By now, the support for OpenMP 3.0 is still in its infancy.

We had quite some difficulties to generate correct and efficient executables with the Intel 11.0 (beta and production) compilers when using tasks. We reported multiple compiler bugs but also found workarounds. Initially, we had to turn off optimization to generate correct executables. Since version 11.1.016 of

the Intel beta compiler we are able to turn the optimization on by **-O3**, but we were forced to disable the production of debugging symbols by omitting the **-g** flag due of yet another bug in the compiler. Fixes for our problems are announced by Intel. The Sun Studio Express Compiler (Version 07/2008) came out a little later than first Intel compiler with tasking support and did not reveal any similar weaknesses when employing tasks.

By now, there are no tools available which may help to check the correctness of threaded programs which use tasks. We tried out Intel's Thread Checker and Sun's Thread Analyze without success, which is not surprising because these tools officially do not support tasking by now.

We also failed to get meaningful hardware counter data with Intel VTune due to many bugs and the inability of VTune to read the debug information from a binary compiled with the Sun Studio compiler. This prevented us from drilling further down into some of the performance peculiarities that we are not yet able to explain satisfactorily.

#### 5 Conclusion

In the context of the simulation of bevel gear cutting processes we compared different approaches of parallelizing recursive algorithms for binary tree traversals using OpenMP with advanced Fortran 90/95.

Recursively nesting of PARALLEL SECTIONS is appealing because of it's simplicity, while the laborious stack implementation [5] performs better on unbalanced trees. The new tasking approach provided by OpenMP 3.0 combines ease of use of the first approach and the scalability of the second, provided that data scoping is handled with care.

We obtained a speed-up of up to 3.86 on the single-socket 8-core multithreaded Niagara 2-based system and up to 3.49 on the dual-socket 4-core Harpertown-based machine for the first routine ("A") and a speed-up of up to 8.59 on the Niagara 2- but only 1.98 on the Harpertown-based system for the second routine ("B").

Future work will include a test of upcoming compiler versions and tuning the runtime environment. Particularly, we want to investigate the matter of limited scalability of the routine B on Harpertown. Further experiments concerning untied tasks, thread placement, and wait policies will be carried out once the compilers mature and generate more reliable code.

#### References

- 1. WZL: Homepage of laboratory for machine tools and production engineering (wzl) of rheinisch-westfälischen technischen hochschule zu aachen,

- http://www.wzl.rwth-aachen.de

- WZL: Calculation of the chip creation parameters for the manufacturing of bevel gears,

- http://www.wzl.rwth-aachen.de/en/cd77f1f9bc96139dc125707e00445cb1.htm

- Brecher, C., Klocke, F., Schröder, T., Rütjes, U.: Analysis and simulation of different manufacturing processes for bevel gear cutting. In: Proceedings of the International Conference on Manufacturing, Machine Design and Tribology (ICMDT 2007), Printed by JSME, Sapporo, Japan (July 2007)

- Klocke, F., Brecher, C., Rütjes, U.: Manufacturing simulation of the cutting process for bevel gears. In: Proceedings of the International Conference on Gears. VDI Berichte, vol. 1904, pp. 865–879. VDI Verlag GmbH, Duesseldorf (2005)

- 5. Kapinos, P.: Diploma thesis of Recursions in the multilevel parallelization of simulating machine tools and cutting processes with openmp (in german) (November 2007), http://www.sc.rwth-aachen.de/Diplom/PaulKapinos.html

- OpenMP ARB: Latest official openmp specifications: Version 3.0 (May 2008), http://www.openmp.org/mp-documents/spec30.pdf

- Terboven, C.: First experiments with tasking in openmp 3.0 (June 2008), http://terboven.spaces.live.com/blog/cnsEA3D3C756483FECB316.entry

# Evaluation of Multicore Processors for Embedded Systems by Parallel Benchmark Program Using OpenMP

Toshihiro Hanawa, Mitsuhisa Sato, Jinpil Lee, Takayuki Imada, Hideaki Kimura, and Taisuke Boku

University of Tsukuba, 1-1-1 Tennodai, Tsukuba 305-8577 Japan {hanawa,msato,taisuke}@cs.tsukuba.ac.jp {jinpil,imada,kimura}@hpcs.cs.tsukuba.ac.jp

Abstract. Recently, multicore technology has been introduced to embedded systems in order to improve performance and reduce power consumption. In the present study, three SMP multicore processors for embedded systems and a multicore processor for a desktop PC are evaluated by the parallel benchmark using OpenMP. The results indicate that, even if the memory performance is low, applications that are not memory-intensive exhibit large speedups by parallelization. The results also indicate a large performance improvement due to parallelization using OpenMP, despite its low cost.

#### 1 Introduction

Recently, the use of embedded systems with complicated functions, such as digital home appliances and car navigation systems, has become widespread. These systems require increasingly higher performance as the functionality of the user interface becomes increasingly higher and the amount of information being processed increases. On the other hand, the power consumption of embedded systems must be reduced in order to extend the operating time of mobile devices and realize more environmentally friendly products. Therefore, multicore technology has been introduced not only for high-end general-purpose processors but also for embedded processors, because multicore is advantageous in terms of performance per watt. On a multicore SMP processor, conventional multi-thread programming using POSIX thread library has been required, or special assembly language code has been inserted at each synchronization point. However, as the applications on embedded system become larger, in order to reduce the development time an easier programming method for parallel processing is required in place of complex programming methods that require and skilled programmers.

OpenMP[1] is a portable programming model that provides a flexible interface for developing parallel applications on shared memory multiprocessors. By inserting a hint for parallelization, called a "directive", into a program written in a conventional programming language, such as C, C++, or Fortran, the OpenMP compiler generates the parallelized code. Recently, OpenMP has become available for several compiler products for desktop computers or servers.

In this way, the development environment of OpenMP can be used broadly. The GNU Compiler Collection (GCC), which is a well-known open-source compiler suite [2], has supported OpenMP since GCC version 4.2. Nevertheless, in the field of embedded systems, a special cross compiler is provided by the vendor, and most of these compilers cannot treat OpenMP directives.

In the present study, we evaluate some embedded multicore processors with a shared memory mechanism by parallel benchmark programs using OpenMP. In addition, we develop the OpenMP implementation using a cross compiling environment for embedded multicore systems. Since embedded multicore processors are widely used, we investigate the following:

- the effect of OpenMP as a programming method, and

- the memory bandwidth and synchronization performance as an SMP multicore processor and their impact on the overall system performance.

#### 2 Multicore Processor for Embedded Systems

In the present study, we evaluate three multicore processors for embedded systems with shared memory: M32700, MPCore, and RP1. Furthermore, as an example of a multicore processor for a desktop PC, the Intel Core2Quad Q6600 is examined for the purpose of comparison.

In the following, we will describe the M32700, the MPCore, and the RP1 in greater detail.

#### 2.1 Renesas Technology M32700

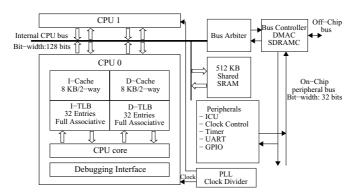

The M32700[3], developed by Renesas Technology, is a dual-core processor embedded with two M32R-II cores.

Figure 1 shows a block diagram of the M32700 processor. The M32R-II core consists of seven-stage pipeline, and each core includes an 8-Kbyte instruction

Fig. 1. Block diagram of the M32700 processor[3]

cache and an 8-Kbyte data cache with two-way set associativity. The data cache is managed by a cache consistency mechanism between the cores. On the M32700 chip, a 512-Kbyte SRAM is shared with two cores via a 128-bit internal bus.

The M32R-II instruction set consists of 32-bit instructions and more frequently used 16-bit instructions. If two 16-bit instructions are located continuously, these instructions can be issued simultaneously depending on the combination of instructions. On the other hand, the M32700 does not have a floating-point function unit.

#### 2.2 ARM/NEC Electronics MPCore

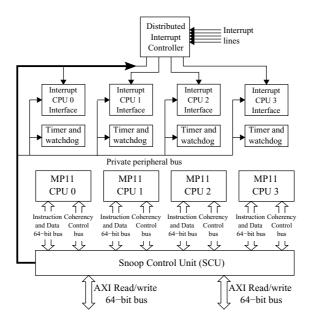

The MPCore[4], developed by ARM and NEC Electronics, is a quad-core processor into which four MP11 cores are embedded. The MPCore is designed as a combination of various function modules called PrimeCells to provide a flexible configuration. Figure 2 shows a block diagram of the MPCore processor.

The MP11 core is an implementation of the ARM11 micro architecture based on ARMv6 instruction set architecture and has an eight-stage, single-issue pipeline. The MP11 core consists of the 32-bit ARM instruction set, the 16-bit Thumb instruction set, the Jazelle instruction set for acceleration of the Java virtual machine, as well as DSP extensions, and SIMD instructions, for example. In the present study, we use the only the 32-bit ARM instruction set.

Each core is connected to a Snoop Control Unit (SCU), and two AXI buses from the SCU are connected to external devices. In the evaluation board used in

Fig. 2. Block Diagram of the MPCore processor[4]

the present study, external peripheral devices, including two AXI bus interfaces for attachment to the MPCore processor and a DRAM controller, are incorporated into a single FPGA chip. Therefore, the external system bus and the DRAM controllers are operated at a clock frequency of 30 MHz. To reduce the influence of the performance degradation due to the slow frequency for the bus clock, in addition to 32-Kbyte instruction and 32-Kbyte data level-1 caches, a level-2 shared-cache of 1 Mbyte is embedded on the MPCore[5].

#### 2.3 Renesas/Hitachi/Waseda University RP1

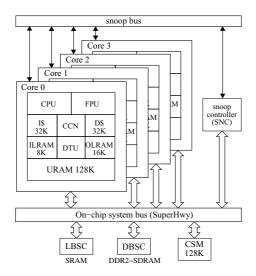

The RP1 processor, developed by Renesas, Hitachi, and Waseda University, is a quad-core processor based on SH-X3 architecture[6]. The RP1 includes four SH-4A cores and performs 4,320 MIPS and 16.8 GFlops at a clock frequency of 600 MHz. Figure 3 shows a block diagram of the RP1 processor.

The SH-4A core consists of an eight-stage pipeline and can issue two 16-bit instructions simultaneously. The RP1 has a dedicated snoop bus for cache consistency, and data transfer for cache coherence control can avoid traffic on the Super Highway (SHwy). The RP1 also includes local memories dedicated to each core that can be accessed with one clock, ILRAM for instructions and OLRAM for data, a local memory that can be accessed with several clocks, URAM, and a centralized shared memory, CSM.

In the present study, we use Linux as the operating system and do not apply the internal memory in the RP1 chip to Linux, so that the RP1 is treated as a conventional SMP processor.

Fig. 3. Block diagram of the RP1 processor[6]

#### 3 Omni OpenMP Compiler

As an OpenMP implementation, Omni OpenMP compiler version 2, which we developed previously, is used. In order to adapt to each multicore architecture, the runtime library must be implemented using spinlock, and the cross compiling environment must be built as described below.

#### 3.1 Implementation of the Runtime Library

When an OpenMP program is compiled using Omni OpenMP compiler, we can choose either mutex\_lock, provided by POSIX thread, or a dedicated spinlock function for specific architecture from the runtime libraries as the mutual exclusion. For this purpose, we implement the runtime libraries using spinlock for each of the multicore processors examined in the present study. Initially, a lock variable is set to 0 and is changed to 1 when the lock is acquired. If the lock variable is already 1, the lock is in use, and the process waits using busy waiting until the release of the lock. At the exit of the critical section, the lock variable reverts to 0, i.e., the unlocked state. In addition, to avoid false sharing of the cache block, lock variables are aligned to the boundary of cache line.

Figure 4 shows the implementation of the spinlock function for each multicore in assembly language. These implementations are performed by referencing the Linux kernel[7].

M32700 M32R provides only bus lock/unlock operations, lock/unlock instructions, as the atomic operation. While the bus is locked, the other processor or peripherals cannot access the bus, which causes degradation of performance. Here, we assume that the address of the lock variable is stored in r0.

To minimize the lock period, after the lock instruction reads the lock variable to r5, the unlock instruction is immediately performed, and the lock variable is set to 1 simultaneously. If r5 is not 0, then the lock is already in use, and r5 returns to the starting point. To avoid the bus contention caused by repeating the lock operation, the lock variable is tested before the second lock operation, and the nop (no-operation) instruction is added.

|   | M32700        |   | MPCore               |   | RP1             |

|---|---------------|---|----------------------|---|-----------------|

| 1 | ldi r4,#1     | 1 | mov r3, #1           | 1 | loop:           |

| 2 | loop:         | 2 | loop:                | 2 | movli.l @r4, r0 |

| 3 | lock r5,@r0   | 3 | ldrex r1, [r0]       | 3 | tst r0, r0      |

| 4 | unlock r4,@r0 | 4 | teq r1, #0           | 4 | bf loop         |

| 5 | bnez r5,loop  | 5 | strexeq r1, r3, [r0] | 5 | mov #1, r0      |

| 6 | exit:         | 6 | teqeq r1, #0         | 6 | movco.l r0, @r4 |

|   |               | 7 | bne loop             | 7 | bf loop         |

|   |               | 8 | exit:                | 8 | exit:           |

Fig. 4. Spinlock codes for each architecture

MPCore ARMv6 architecture provides the Exclusive Load, ldrex instruction, and the Exclusive Store strex instruction. Here, we assume that the address of the lock variable is stored in r0.

Ldrex reads the lock variable to r3, and then the operation mode is changed to the exclusive access mode. In line 4, if r1 is 0, then the Z (Zero) flag is set. Hereinafter, suffix eq indicates that the instruction is executed if and only if the Z flag is set. Otherwise, the instruction is replaced with nop. In line 5, when the Z flag is set, that is, when the lock acquisition is successful, strex tries to write the value 1 into the lock variable. If another processor has not written to the lock variable until the exclusive access mode, then the write operation by strex is successful, and r1 is set to 0. Otherwise, r1 becomes 1. In line 6, teqeq checks whether store is successful. If the lock cannot be acquired, or the store is unsuccessful, the operation returns from line 7 to line 3.

RP1 On SH4A architecture, Move Linked, movli, and Move Conditional, movco instructions are available. The movli and movco operations are similar to Exclusive Load and Exclusive Store, respectively, of the MPCore. Here, we assume that the address of the lock variable is stored in r4.

Movli reads the lock variable to r0 implicitly. Unless the value r0 is 0, the lock acquisition is retried in lines 3 and 4. Movco tries to set the lock variable to 1. The T (True) flag is set if this is successful. Otherwise, the T flag is reset, and the operation returns from line 7 to line 2 movli.

#### 3.2 Cross Compiling Environment

The Omni OpenMP compiler consists of a front-end part, a translation part, and a runtime library. The front-end part converts a C or Fortran program to a common intermediate language. The translation part translates the OpenMP directives into a normal multithreaded C program using POSIX threads.

In the case of cross compiling, similar to the native compiler, the front-end part and the translation part can be executed on the host PC (x86) because these processes and codes are architecture-independent. Finally, the cross compiler for the target architecture generates the target binary linked with the runtime library described in Section 3.1 from the multithreaded code.

#### 4 Performance Evaluation

#### 4.1 Evaluation Environment

In the present study, we evaluate four multicore processors described in Section 2. Table 1 shows the specifications and the operating environment. We adopt Linux 2.6 as the operating system. These embedded systems start up via 100-Mbps Ethernet using the Network File System (NFS), and the Q6600 in the desktop PC uses the local file system.

As the OpenMP implementation, Omni OpenMP compiler Version 2 is commonly used for all platforms in the present study. For the back-end compiler, we

| Processor          | M32700           | MPCore       | RP1          | Q6600                 |

|--------------------|------------------|--------------|--------------|-----------------------|

| # of Cores         | 2                | 4            | 4            | 4                     |

| Frequency          |                  |              |              |                       |

| Core/Int./Ext. Bus | 300/75/75        | 210/210/30   | 600/300/50   | $2.4~\mathrm{GHz}$    |

| , ,                | MHz              | MHz          | MHz          |                       |

| Cache L1: I+D      | 8K+8K/2-way      | 32K + 32K/4- | 32K+32K/4-   | 32K + 32K/8-          |

|                    |                  | way          | way          | way                   |

| L2:                |                  | 1M/8-way     | _            | $4M \times 2/16$ -way |

| Line size (byte)   | 16               | 32           | 32           | 64                    |

| Memory             | 32-Mbyte         | 256-Mbyte    | 128-Mbyte    | 2-Gbyte               |

| Type               | SDRAM            | DDR          | DDR2-600     | DDR2-800              |

| Clock              | 100 MHz          | 30  MHz      | 300  MHz     | 400  MHz              |

| OS                 | Linux 2.6.25     | Linux 2.6.19 | Linux 2.6.16 | Linux 2.6.18          |

| uname -m           | m32r             | armv61       | sh4a         | i686                  |

| C Compiler         | gcc 4.1.2        | gcc 4.1.1    | gcc 3.4.5    | gcc 4.1.2             |

|                    | 20061115         |              | 20060103     | 20061115              |

| Target             | -m32r2           | -mcpu=mpcore | -m4a         | -march=nocona         |

| C Library          | glibc 2.3.6.ds1- | glibc 2.3.6  | glibc 2.3.3  | glibc 2.3.6.ds1-      |

|                    | 13               |              |              | 13.etch5              |

| Pthread            | Linuxthreads     | NPTL 2.3.6   | Linuxthreads | NPTL 2.3.6            |

|                    | 0.10             |              | 0.10         |                       |

Table 1. Evaluation environment

use various versions of gcc C compiler, as listed in Table 1. We also use glibc as the standard C library. However, each environment provides a POSIX thread library through different implementations.

LinuxThreads is the first implementation of POSIX thread on Linux. In order to manage thread creation or thread termination, a manager thread is required independently of the computation thread, and operations related to synchronization are implemented by signal. In contrast, the Native POSIX Threads Library (NPTL) is an implementation that was developed to solve the problem of LinuxThreads. NPTL uses futex, which stands for fast user-level locking mechanism. In the case of the RP1, although the TAS (test-and-set) instruction is not suitable for the SMP environment, the LinuxThreads library contains TAS (test-and-set) instructions. Therefore, we rewrite the library using MOVLI/MOVCO instructions and replace the pthread library of the system with the improved library described herein.

#### 4.2 Benchmark

Next, we explain the parallel benchmarks used in the present study.

The MiBench suite [8] is a free benchmark suite for embedded processors that emulates the benchmark suite developed by the EEMBC (Embedded Microprocessor Benchmark Consortium)[9]. MiBench includes six categories, namely, Automotive and Industrial Control, Consumer Devices, Office Automation,

Networking, Security, and Telecommunications, and consists of 35 benchmarks. In the present study, we consider the major algorithms to parallelize benchmarks using OpenMP for typical applications on embedded systems. We choose Susan Smoothing (SS), the image-processing algorithm from Automotive@category, Blowfish Encrypt (BF) from Security category, and FFT from Telecommunications category, and parallelize these benchmarks using OpenMP.

In addition, we attempt to confirm the performance of target multicore processors using existing scientific applications. We use some benchmarks from the NAS Parallel Benchmark (NPB)[10], including IS and CG. IS in NPB3.3-OMP[11] is written in C language with OpenMP. Although CG in NPB is described in Fortran, Omni OpenMP provides a modified version of CG, which is translated into C language and uses OpenMP directives as the sample.

MediaBench is a benchmark for embedded multimedia applications [12]. We use the parallelized version using OpenMP of mpeg2encode [13]. Since we consider multimedia streaming to be one of the most suitable applications for embedded multicore processors, we choose this benchmark.

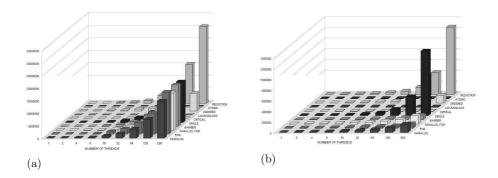

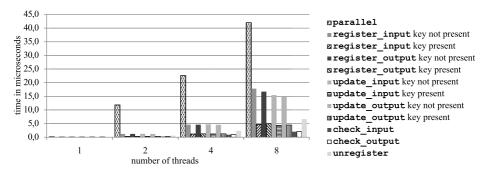

#### 4.3 Performance Evaluation for Synchronization

First, we preliminarily evaluate each system for synchronization using syncbench of the EPCC micro benchmark[14]. Table 2 shows the results for syncbench. The M32700 is investigated using two cores, and the other processors are investigated using up to four cores. As a result, the M32700 and the RP1 using LinuxThreads as the POSIX thread library have very low performance in the cases of "single," "critical," "lock/unlock," and "atomic" with mutex\_lock, which indicates that the signal handling degrades the performance when rendezvous occurs among the threads. To solve this problem, we introduce the spinlock mechanism for synchronization (in place of mutex\_lock). The results indicate that the introduction of the spinlock in LinuxThreads results in an extreme speedup. For

| -            | M32   | 700   | MPC        | Core  | RF         | P1    | Core2Quad  |       |

|--------------|-------|-------|------------|-------|------------|-------|------------|-------|

|              | (2 P  | U)    | (4 P       | U)    | (4 P       | U)    | (4 PU)     |       |

|              | Mutex | Spin  | Mutex Spin |       | Mutex Spin |       | Mutex Spin |       |

| parallel     | 392.2 | 376.8 | 436.5      | 434.8 | 107.8      | 107.2 | 2.80       | 2.25  |

| for          | 18.5  | 13.6  | 7.46       | 6.15  | 1.66       | 1.42  | 0.364      | 0.372 |

| parallel for | 399.7 | 383.6 | 436.3      | 435.7 | 108.2      | 107.7 | 3.71       | 2.47  |

| barrier      | 14.1  | 10.7  | 6.11       | 5.98  | 1.13       | 0.867 | 0.301      | 0.316 |

| single       | 50.8  | 9.87  | 3.14       | 3.12  | 295.1      | 1.53  | 4.54       | 0.859 |

| critical     | 273.5 | 3.15  | 0.921      | 0.837 | 128.2      | 0.190 | 1.31       | 0.129 |

| lock/unlock  | 273.1 | 2.51  | 1.03       | 0.962 | 121.0      | 0.174 | 1.41       | 0.131 |

| ordered      | 8.64  | 7.08  | 1.50       | 1.33  | 0.584      | 0.598 | 0.191      | 0.168 |

| atomic       | 241.0 | 0.501 | 0.894      | 0.893 | 121.0      | 0.365 | 0.474      | 0.307 |

| reduction    | 401.9 | 387.1 | 443.9      | 443.8 | 327.0      | 109.1 | 6.13       | 3.35  |

**Table 2.** Results of EPCC syncbench (Unit:  $\mu$ s)

example, the speedup by spinlock is 482 in the case of "atomic" on the M32700, and 695 in the case of "lock/unlock" on the RP1. On the MPCore using NPTL, in the case of "ordered", the performance of spinlock increases slightly (1.12 times faster) compared with that of mutex\_lock. Based on these results, hereinafter, we use only spinlock for synchronization. In the case of embedded processors, "parallel," "parallel for," and "reduction" directives, which include the element of "parallel" directive, the execution time is relatively large. When the "parallel" directive is assigned, some threads are generated so that the program can be performed in parallel, and memory access is frequent. The MPCore, for which the access time to DRAM is slowest, requires the longest execution time for parallel directives. Naturally, the parallel region should be assigned to the largest section possible in order to reduce the overhead for thread assignment.

#### 4.4 Evaluation by Parallel Benchmarks Using OpenMP

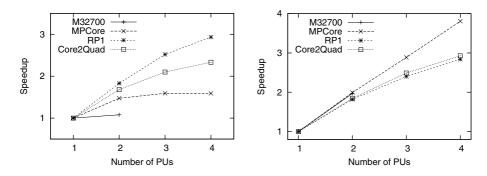

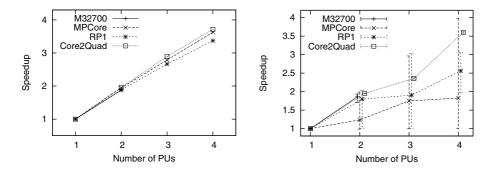

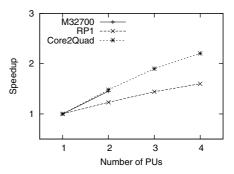

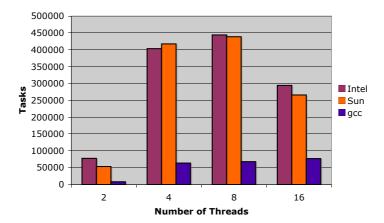

Next, we evaluate the multicore processors using parallel benchmarks. First, we use NAS Parallel Benchmarks. Figure 5 shows the speedup of IS (Class W). In addition, Table 3 shows the actual execution times for all of the benchmarks. NPB IS is a memory-intensive program. Since the embedded processors have low bandwidth for memory access, the MPCore with four cores only achieves a speedup of 1.6 times, whereas the speedup of the M32700 is 1.1 times. In contrast, the speedup of the RP1 with four cores is 2.9 times. The RP1 has a dedicated bus for the snoop cache control, and the above results indicate that the mechanism for cache control in the RP1 is effective. Figure 6 shows the speedup of CG  $(1,400\times1,400,{\rm sparse\ matrix})$ . On this benchmark, the speedups of both the RP1 and the Q6600 with four cores are 2.8 times. The reason for this is that CG is a computation-intensive benchmark. On the other hand, in the case of

| Processor | PU | IS    | CG    | $Susan\_s$ | FFT    | Blowfish             | Mpeg2encode |

|-----------|----|-------|-------|------------|--------|----------------------|-------------|

| M32700    | 1  | 4.66  | 183.5 | 22.1       | 19.6   | 175.3                | 1143.8      |

|           | 2  | 4.32  | 93.2  | 11.8       | 10.5   | 94.3 (90.6–102.4)    | 788.0       |

| MPCore    | 1  | 11.3  | 31.0  | 21.7       | 3.19   | 138.9                | _           |

|           | 2  | 7.66  | 15.6  | 11.2       | 1.71   | 112.4 (69.8–140.6)   | _           |

|           | 3  | 7.09  | 10.8  | 7.80       | 1.31   | 79.4 (46.8–139.8)    |             |

|           | 4  | 7.09  | 8.15  | 5.99       | 1.03   | 76.1 (34.9–139.3)    |             |

| RP1       | 1  | 4.14  | 4.43  | 8.49       | 0.280  | 60.2                 | 57.4        |

|           | 2  | 2.26  | 2.44  | 4.51       | 0.147  | 33.5 (29.5–60.0)     | 46.6        |

|           | 3  | 1.64  | 1.85  | 3.18       | 0.107  | 31.6 (19.9–59.8)     | 39.8        |

|           | 4  | 1.41  | 1.56  | 2.52       | 0.085  | 23.5 (19.7–30.6)     | 35.9        |

| Q6600     | 1  | 0.06  | 0.215 | 0.933      | 0.0076 | 6.12                 | 5.47        |

|           | 2  | 0.036 | 0.116 | 0.476      | 0.0048 | 3.14 (3.13 - 3.15)   | 3.69        |

|           | 3  | 0.029 | 0.086 | 0.322      | 0.0065 | $2.59 \ (2.58-2.62)$ | 2.88        |

|           | 4  | 0.026 | 0.073 | 0.251      | 0.0063 | $1.70 \ (1.69-1.71)$ | 2.48        |

Table 3. Results of Performance Evaluation (Unit: seconds)

Fig. 5. Speedup of NPB IS (CLASS=W)

Fig. 6. Speedup of CG

the MPCore, the speedup is 3.8 times. The cache efficiency appears to increase because the L2 cache is shared among four cores.

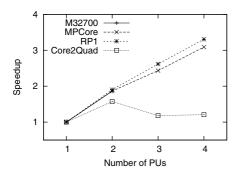

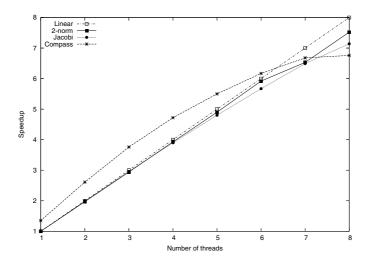

Next, we investigate the speedup in the case of MiBench. Here, we introduce MiDataSets, which is a collection of various workloads for MiBench[15]. We adopt 19.pgm for SS, 4.txt for BF from MiDataSets, and the large dataset in MiBench is used for FFT (nwave=6, nsample=65,536). In addition, we change the algorithm in BF from the CFB64 mode to the ECB mode. Figures 7, 8, and 9 show the speedup of SS, BF, and FFT, respectively. The speedup of SS is from 3.4 to 3.7 times due to high parallelism. The parallel version of BF performs the following operations in a pipelined manner: read 40 bytes from input file, encrypt 100 times, then write 40 bytes to output file. Since BF indicates scattering results of the execution time (except for the Q6600), we append the minimum and maximum execution times to the average time. This dispersion appears to be caused by the influence of the NFS because the results for the Q6600 are stable. As a result of the slight dependency among only 8 bytes in the ECB mode, in the best case of all the trial, we can obtain a speedup of 4.0 times with four cores on the MPCore, and a speedup of 3.0 times with three cores on the RP1.

Fig. 7. Speedup of Susan (smoothing)

Fig. 8. Speedup of Blowfish

Fig. 9. Speedup of FFT

Fig. 10. Speedup of Mpeg2encode

For FFT on the RP1 with four cores, a speedup of 3.3 times is obtained due to high parallelism. For the Q6600, the speedup is degraded in the case of three or four cores, as compared to two cores, because the working set is so small for the Q6600 that the synchronization cost becomes dominant. Table 4 shows the cost of modification for OpenMP. Parallelization through the use of OpenMP is quite simple, and involves only the insertion of a small number of OpenMP directives.

Finally, Figure 10 shows the speedup of mpeg encoding. We cannot execute this benchmark on the MPCore because of a fatal error. Although the speedup on the Q6600 with four cores is 2.2 times, in the case of the RP1 with four cores, the speedup is only 1.6 times due to the overhead of file operation via NFS. In the case of the M32700, there is no degradation of the performance because the execution time is sufficiently long due to the software emulation of floating point operations.

| Benchmark | Change                             |

|-----------|------------------------------------|

| SS        | add 6 directives                   |

| BF        | add 9 directives & modify 12 lines |

| FFT       | add 4 directives                   |

Table 4. Modification Cost for OpenMP

#### 5 Related Work

Several embedded multicore processors had been evaluated indivisually. Hotta, et al. [13] evaluated the M32700 by mpeg2enc in MediaBench parallelized with OpenMP. Blume, et al. [16] evaluated the MPCore using several applications parallelized with OpenMP. Seo, et al. [17] studied OpenMP directive extension for BlackFin 561 Dual-Core processor, and they modified EEMBC benchmarks[9] for parallel version using OpenMP.

Miyamoto, et al. [18] evaluated Fujitsu FR1000 processor and the RP1 using multimedia applications parallelized automatically by OSCAR compiler which they developed.

Several different kinds of embedded multicore processors had never been evaluated simultaneously by the parallel benchmark using OpenMP.

#### 6 Conclusion

In the present study, we evaluated the performance of four multicore processors, namely, the M32700, the MPCore, and the RP1 for embedded systems, and the Core2Quad Q6600 for a desktop PC. After we investigated the synchronization performance using syncbench of the EPCC micro benchmark, we used various benchmarks, including the NAS Parallel Benchmarks, MediaBench, and MiBench, which are parallelized by OpenMP.

As a result, although embedded multicore processors have larger synchronization cost and slower memory performance than multicore processors for desktop PC, the spinlock mechanism enables embedded multicore processors to improve the synchronization performance. Moreover, according to the parallel benchmarks using OpenMP, the performance became higher as the number of cores increased for the case in which several OpenMP directives were inserted into the source code. Therefore, OpenMP is very useful for parallelizing embedded applications as well as scientific applications on HPC. On the other hand, major hurdles remain with respect to the use of OpenMP for embedded systems. For example, parallel processing using OpenMP is too difficult to satisfy real-time restriction. To apply OpenMP to embedded systems, some extensions for OpenMP directives will be required, including functions such as real-time processing and power-awareness.

In the future, the effect of spinlock for synchronization under multiple parallelworkloads should be examined. In addition, most multicore processors include fast internal memories on the chip, and we will consider using these internal memories to speedup synchronization. Furthermore, we will investigate the transition of power consumption of each multicore processor system for various numbers of cores.

### Acknowledgment

The authors would like to thank Renesas Technology Corporation for providing the M3T-M32700UT. The RP1 multicore-chip and its runtime environment used in the present study were developed by Waseda University (Kasahara-Kimura Laboratory), Renesas Technology Corporation, and Hitachi, Ltd. as part of the NEDO project entitled "Multi-core Processor Technologies for Real Time Consumer Electronics." The present study was supported in part by the JST/CREST program entitled "Computation Platform for Power-aware and Reliable Embedded Parallel Processing System" in the research area of "Dependable Embedded Operating Systems for Practical Use."

#### References

- 1. The OpenMP Architecture Review Board: The OpenMP API specification for parallel programming,

- http://openmp.org/wp/

- Free Software Foundation: GCC, the GNU Compiler Collection, http://gcc.gnu.org/

- 3. Kaneko, S., et al.: A 600MHz Single-Chip Multiprocessor with 4.8GB/s Internal Shared Pipelined Bus and 512kB Internal Memory. In: International Solid-State Circuits Conference (ISSCC), vol. 1, pp. 254–255 (2003)

- 4. ARM Limited: ARM11 MPCore Processor Technical Reference Manual (2006)

- 5. ARM Limited: Using a CT11MPCore with the RealView Emulation Baseboard (2006)

- Yoshida, Y., et al.: A 4320MIPS Four-Processor Core SMP/AMP with Individually Managed Clock Frequency for Low Power Consumption. In: International Solid-State Circuits Conference (ISSCC), pp. 100–590 (2007)

- 7. The Linux Kernel Archives, http://kernel.org/

- 8. Guthaus, M., et al.: MiBench: A free, commercially representative embedded benchmark suite. In: IEEE 4th Annual Workshop on Workload Characterization (2001)

- 9. The Embedded Microprocessor Benchmark Consortium: EEMBC The Embedded Microprocessor Benchmark Consortium, http://www.eembc.org/

- Bailey, D., et al.: The NAS Parallel Benchmarks. RNR Technical Report RNR-94-007, NASA Ames Research Center (1994)

- Jin, H., Frumkin, M., Yan, J.: The OpenMP Implementation of NAS Parallel Benchmarks and Its Performance. NAS Technical Report NAS-99-011, NAS System Division NASA Ames Research Center (1999)

- 12. Lee, C., Potkonjak, M., Mangione-Smith, H.: MediaBench: A Tool for Evaluating and Synthesizing Multimedia and Communications Systems. In: International Symposium on Microarchitecture (Micro-30), pp. 330–335 (1997)

- 13. Hotta, Y., Sato, M., Nakajima, Y., Ojima, Y.: OpenMP Implementation and Performance on Embedded Renesas M32R Chip Multiprocessor. In: Sixth European Workshop on OpenMP (EWOMP 2004), pp. 37–42 (2004)

- Bull, J.M.: Measuring Synchronisation and Scheduling Overheads in OpenMP. In: European Workshop on OpenMP (EWOMP 1999), pp. 99–105 (1999)

- Fursin, G., Cavazos, J., O'Boyle, M., Temam, O.: MiDataSets: Creating The Conditions For A More Realistic Evaluation of Iterative Optimization. In: De Bosschere, K., Kaeli, D., Stenström, P., Whalley, D., Ungerer, T. (eds.) HiPEAC 2007. LNCS, vol. 4367, pp. 245–260. Springer, Heidelberg (2007)

- Blume, H., von Livonius, J., Rotenberg, L., Noll, T.G., Bothe, H., Brakensiek, J.: OpenMP-based parallelization on an MPCore multiprocessor platform - A performance and power analysis. Journal of Systems Architecture 54(11), 1019–1029 (2008)

- 17. Seo, H., Kim, S.W.: OpenMP Directive Extension for BlackFin 561 Dual Core Processor. In: Sixth IEEE International Conference on Computer and Information Technology (CIT 2006), p. 49 (2006)

- Miyamoto, T., Asaka, S., Mikami, H., Mase, M., Wada, Y., Nakano, H., Kimura, K., Kasahara, H.: Parallelization with Automatic Parallelizing Compiler Generating Consumer Electronics Multicore API. In: International Symposium on Parallel and Distributed Processing with Applications (ISPA 2008), pp. 600–607 (2008)

# Extending Automatic Parallelization to Optimize High-Level Abstractions for Multicore\*

Chunhua Liao<sup>1</sup>, Daniel J. Quinlan<sup>1</sup>, Jeremiah J. Willcock<sup>2</sup>, and Thomas Panas<sup>1</sup>

Center for Applied Scientific Computing Lawrence Livermore National Laboratory Livermore, CA 94551 {liao6,quinlan1,panas2}@llnl.gov <sup>2</sup> Computer Science Department Indiana University Lindley Hall Room 215 150 S. Woodlawn Ave. Bloomington, IN, 47404 jewillco@osl.iu.edu

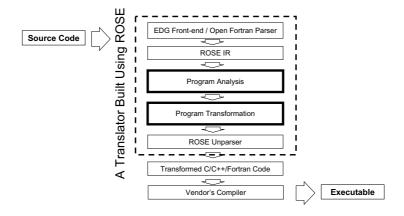

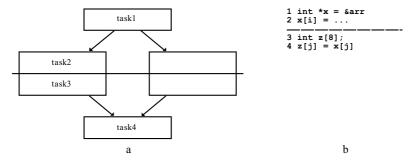

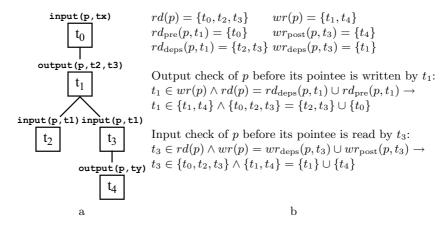

**Abstract.** Automatic introduction of OpenMP for sequential applications has attracted significant attention recently because of the proliferation of multicore processors and the simplicity of using OpenMP to express parallelism for shared-memory systems. However, most previous research has only focused on C and Fortran applications operating on primitive data types. C++ applications using high-level abstractions. such as STL containers and complex user-defined types, are largely ignored due to the lack of research compilers that are readily able to recognize high-level object-oriented abstractions and leverage their associated semantics. In this paper, we automatically parallelize C++ applications using ROSE, a multiple-language source-to-source compiler infrastructure which preserves the high-level abstractions and allows us to unambiguously leverage their known semantics. Several representative parallelization candidate kernels are used to explore semantic-aware parallelization strategies for high-level abstractions, combined with extended compiler analyses. Those kernels include an array-based computation loop, a loop with task-level parallelism, and a domain-specific tree traversal. Our work extends the applicability of automatic parallelization to modern applications using high-level abstractions and exposes more opportunities to take advantage of multicore processors.

#### 1 Introduction

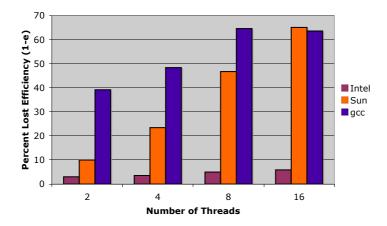

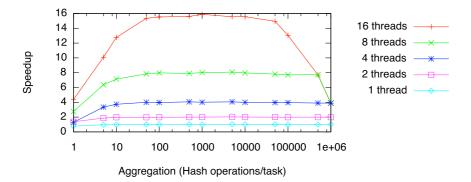

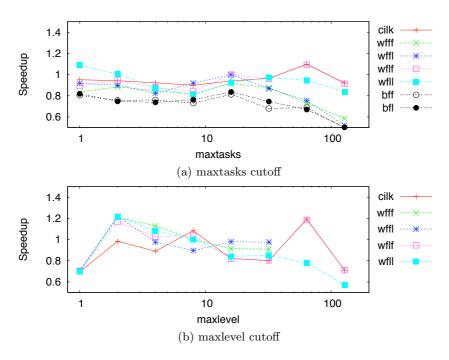

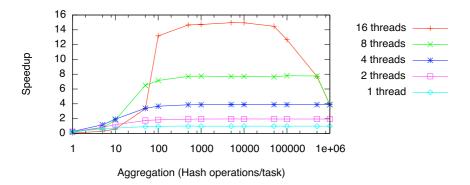

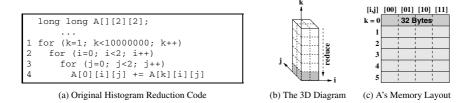

Today's multicore processors have been forcing application developers to parallelize legacy sequential codes and/or write new parallel applications if they